英特尔展示 3D 堆叠 CMOS 晶体管技术:在 60nm 栅距下实现 CFET

英特尔展示 3D 堆叠 CMOS 晶体管技术:在 60nm 栅距下实现 CFET

IT 之家 12 月 10 日消息,由于当下摩尔定律放缓,堆叠晶体管概念重获关注,IMEC (比利时微电子研究中心)于 2018 年提出了堆叠互补晶体管的微缩版 CFET 技术(IT 之家注:即垂直堆叠互补场效应晶体管技术,业界认为 CFET 将取代全栅极 GAA 晶体管技术),英特尔和台积电也都进行了跟进。

在今年的 IEEE 国际电子器件会议(IEDM 2023)上,英特尔展示了多项技术突破,并强调了摩尔定律的延续和演变。

首先,英特尔展示了其中 3D 堆叠 CMOS(互补金属氧化物半导体)晶体管方面取得的突破。

简单来说,研究人员通过将 3D 堆叠 CMOS 晶体管与背面供电和背面接触相结合,实现了业界首次在缩小至 60 nm 的栅极间距下的 CFET。

▲ 英特尔示意图

此外,该公司还报告了最近在背面供电技术方面的研发突破的扩展路径,如背面接触(backside contacts),并且首次演示了在同一 300mm 晶圆上(相对于同一封装而言)实现大规模集成硅晶体管和氮化镓(GaN)晶体管。

英特尔这也是其面向未来节点的下一代晶体管扩展的突破性技术进展,从而再次延续了摩尔定律概念。

除了改善背面供电和采用新颖的二维通道材料外,英特尔还致力于实现到 "2030 年将摩尔定律扩展到单个封装中包含一万亿个晶体管 " 的目标。

最近,英特尔还宣布了其最新的工艺技术路线图,强调了公司在持续扩展方面的创新,包括 PowerVia 背面供电,以及用于先进封装的玻璃基板和 Foveros Direct 等方面,而这些技术预计将在本十年内投入生产。

英特尔表示,这凸显了该公司在全栅晶体管领域的领导地位,并展示了该公司在 RibbonFET 之外的创新能力,从而使其进一步领先于竞争对手。

英特尔高级副总裁兼组件研究部总经理 Sanjay Natarajan 表示," 随着我们进入 Angstrom 时代以及确定四年五个节点的目标,持续创新已经变得比以往任何时候都关键。在 IEDM 2023 上,英特尔展示了其在推动摩尔定律的研究进展方面所取得的进展,强调了我们为下一代移动计算提供进一步扩展和高效供电的能力。"

英特尔认为,他们已经超越了 " 四年五个节点 " 的目标,并确定了继续使用背面供电技术进行晶体管扩展所需的关键研发领域:

英特尔 PowerVia 将在 2024 年具备生产条件,这是业界首次实现背面供电的案例。在 IEDM 2023 上,组件研究部门确定了中 PowerVia 之外延续和扩展背面供电技术的途径,以及实现这些途径所需的关键工艺进步。此外,这项工作还强调了使用背面接触和其他新颖的垂直互连技术来实现更高效的器件堆叠。

在 IEDM 2022 上,英特尔专注于性能增强和构建可行的 300 毫米 GaN-on-silicon 晶圆路径。今年,该公司正在推进硅和 GaN 的工艺集成。英特尔现在已经成功展示了一种名为 "DrGaN" 用于电源传输的高性能大规模集成电路解决方案。英特尔研究人员率先证明该技术性能良好,并且有可能使电力传输解决方案能够跟上未来计算的功率密度和效率需求。

过渡金属二硫属化物(TMD)二维通道材料为缩小晶体管物理栅长度至 10nm 以下提供了独特的机会。在 IEDM 2023 上,英特尔将演示高迁移率 TMD 晶体管的原型,包括 CMOS 的关键组成部分 NMOS(n 沟道金属氧化物半导体)和 PMOS(p 沟道金属氧化物半导体)。英特尔还展示了世界上第一个全栅极环绕(GAA)二维 TMD PMOS 晶体管,以及世界上第一个在 300 毫米晶圆上制造的二维晶体管。

-

- 最近杭州街头突然出现…有人居然捡去泡酒,网友好奇:能吃?

-

2023-12-13 11:43:53

-

- 对统计造假“零容忍”

-

2023-12-13 11:41:37

-

- 美国参议员指控,中国大蒜构成重大国家安全风险

-

2023-12-13 11:39:21

-

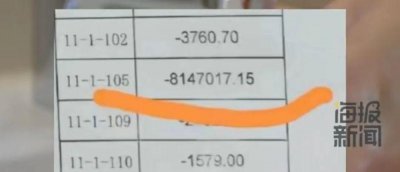

- “倾家荡产不够水费”,业主被物业催缴 800 万!自来水公司回应…

-

2023-12-13 11:37:05

-

- 中国用人民币购买伊朗石油首单后,美国人呼吁让美国退回到金本位

-

2023-12-11 07:00:47

-

- 2032年奥运会在哪个国家举办(卡塔尔申办2032年奥运会:他们的钱,是国际奥委

-

2023-12-11 06:58:31

-

- 佳能是哪个国家的(日本的单反为何能独领风骚?为什么中国就造不出来呢?)

-

2023-12-11 06:56:15

-

- 现在的中国在世界上处于什么地位?

-

2023-12-11 06:54:00

-

- 河北柏乡藏着千年“神”花,被称为世界牡丹活化石,很是传奇!

-

2023-12-11 06:51:44

-

- 邯郸属于哪个省(邯郸市的区划调整,河北省的第三大城市,为何有18个区县?)

-

2023-12-11 06:49:28

-

- 世界十大禁养猛犬排行榜 藏獒排第五第一是谁?

-

2023-12-11 06:47:12

-

- 千岛之国是哪个国家(秀丽迷人的千岛之国——印度尼西亚)

-

2023-12-11 06:44:56

-

- 战舰世界战舰排名 战列舰实力排名一览

-

2023-12-11 06:42:40

-

- 今夜,美国大战伊朗

-

2023-12-11 06:40:24

-

- 济南市行政区划调整示意图:撤销莱芜市,设立莱芜区和钢城区

-

2023-12-09 19:15:59

-

- 网友建议哈尔滨文旅取消狗拉雪橇,12345:目前没接到反馈,会反映给相关承办

-

2023-12-09 19:13:43

-

- 国家统计局一二三线城市划分

-

2023-12-09 19:11:27

-

- 来了!北京市116家体检机构可提供体检服务,附名单

-

2023-12-09 19:09:11

-

- 周口市民坐几路车去高铁站呢?你想知道的都在这了

-

2023-12-09 19:06:55

-

- 重庆市民注意:96007来电一定要及时接听

-

2023-12-09 19:04:39

田明建国门案真实原因(由驻京郊某部的一名连长田建明引起)

田明建国门案真实原因(由驻京郊某部的一名连长田建明引起) 甘蔗上绑香蕉是什么意思 甘蔗上绑着香蕉是什么意思

甘蔗上绑香蕉是什么意思 甘蔗上绑着香蕉是什么意思